#### **Applicable for WLC1115**

#### **About this document**

#### **Scope and purpose**

This document provides design guidelines for the WLC1115-based power transmitter solution board for wireless charger (WLC) applications.

#### **Intended audience**

Wireless transmitter hardware designers using WLC1115 wireless transmitter with integrated USB Type-C PD controller.

#### Table of contents

#### **Table of contents**

| Abou  | ıt this document                                       | 1  |

|-------|--------------------------------------------------------|----|

| Table | e of contents                                          | 2  |

| 1     | About WLC1115                                          | 3  |

| 1.1   | WLC1115 features and applications                      | 3  |

| 1.1.1 | Typical applications                                   | 3  |

| 1.1.2 | Features                                               | 3  |

| 1.2   | WLC1115 in wireless transmitter application            | 4  |

| 1.3   | MP A11 15 W power transmitter board (REF_WLC_TX15W_C1) | 5  |

| 2     | Hardware design                                        | 7  |

| 2.1   | Buck power stage                                       |    |

| 2.1.1 | Inductance requirement and selection                   | 9  |

| 2.1.2 | ·                                                      |    |

| 2.1.3 |                                                        |    |

| 2.1.4 |                                                        |    |

| 2.1.5 |                                                        |    |

| 2.1.6 | •                                                      |    |

| 2.1.7 | Type 2 compensator for buck stage                      |    |

| 2.2   | Inverter power stage                                   |    |

| 2.2.1 | Transmitter coil selection                             |    |

| 2.2.2 |                                                        |    |

| 2.2.3 | ·                                                      |    |

| 2.2.4 | <b>o</b>                                               |    |

| 2.3   | Control section                                        |    |

| 2.3.1 | Q factor estimation with WLC1115                       |    |

| 2.3.2 | •                                                      |    |

| 2.3.3 |                                                        |    |

| 2.3.4 | ·                                                      |    |

| 2.3.5 |                                                        |    |

| 2.3.6 |                                                        |    |

|       |                                                        |    |

| 3     | Design example – 15 W transmitter board                |    |

| 4     | PCB layout guidelines                                  |    |

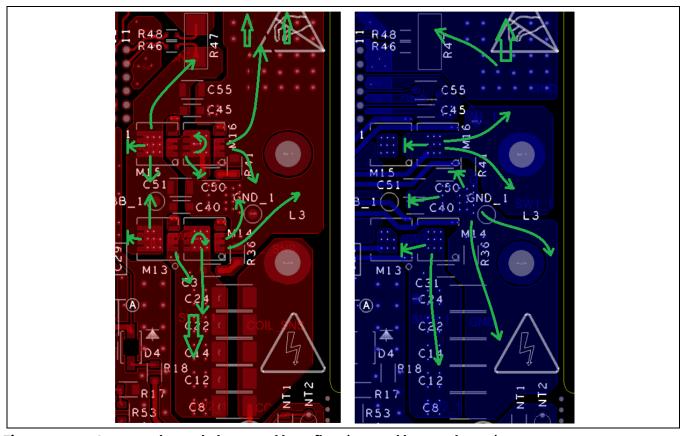

| 4.1   | Power section                                          |    |

| 4.1.1 | Buck regulator                                         |    |

| 4.1.2 |                                                        |    |

| 4.1.3 | , , , , , , , , , , , , , , , , , , , ,                |    |

| 4.2   | Analog section                                         |    |

| 4.2.1 | Demodulator (voltage path and gain stage)              |    |

| 4.2.2 | 9                                                      |    |

| 4.2.3 | Ç                                                      |    |

| 4.3   | Digital section                                        |    |

| 4.4   | Thermal management                                     |    |

| 4.5   | Package footprint design guidelines                    | 45 |

| 5     | Schematic and PCB layout review checklist              | 46 |

| Acror | nyms/Abbreviations                                     | 49 |

|       | rences                                                 |    |

|       |                                                        |    |

| kevis | sion history                                           | 52 |

#### **About WLC1115**

#### 1 About WLC1115

Wireless power transmission, based on loosely coupled inductive power transfer, is a widely used near-field power conversion topology. These power transfer systems are common in consumer appliances such as electric toothbrushes or cell phone chargers, medical devices (power supply and implantable devices), and automotive (in-cabin charger) applications. The Qi wireless power topology utilizes series LC resonance tanks on both transmitter and receiver halves of the wireless power transfer system. The resonant topology offers low EMI along with ZVS turn-on of transmitter-side FETs and receiver-side rectifier FETs. The in-band communication between the transmitter and receiver sections offers a compact solution for wireless charging in low-power consumer applications.

WLC1115 is a highly integrated, Qi-compliant wireless transmitter with integrated USB Type-C power delivery (PD). It complies with the latest USB Type-C, WPC and PD specifications and has integrated gate drivers for buck and inverter power stage MOSFETs. It also includes hardware-controlled protection features on the VBUS. WLC1115 supports a wide input voltage range (4 to 24 V). The single-chip solution provides system control and in-band communication (FSK modulation and ASK demodulation) with minimal external circuits.

#### 1.1 WLC1115 features and applications

#### 1.1.1 Typical applications

- Wireless charging pads for extended power profile (EPP) (15 W) and basic power profile (BPP) (5 W)

- Smart speakers

- Portable accessories

- Furniture and home goods

- Docking stations

#### 1.1.2 Features

- Qi v1.3.x compliant transmitter (MP-A11 coil)

- Integrated USB-PD controller

- Supports latest USB-PD 3.1 version

- Programmable power supply (PPS) mode

- Configurable resistors (R<sub>P</sub>, R<sub>D</sub>)

- Support for USB-PD legacy charging protocols like QC 2.0/3.0 and AFC

- Integrated buck converter controller for VBRIDGE (VBRG)

- Integrated gate drivers for buck converter and inverter

- Integrated Q factor detection

- Integrated FSK modulator

- Wide input voltage range: 4.5 to 24 V

- Communication ports: I<sup>2</sup>C, UART

- Protection

- Overcurrent protection (OCP), overvoltage protection (OVP)

- Supports overtemperature protection through integrated ADC circuit and internal temperature sensor

- Temperature range

- o −40°C to +105°C extended industrial temperature range

- Package

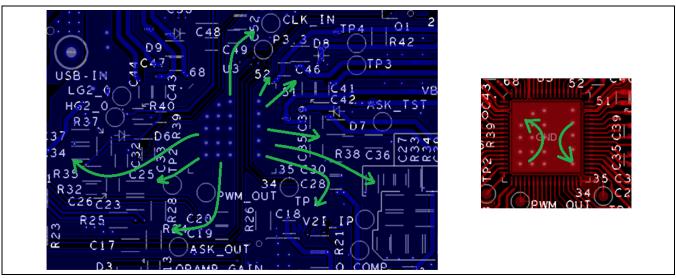

- o 68-pin QFN 8.0 x 8.0 x 0.65 mm LD68B 5.7 x 5.7 mm E-PAD

#### **Applicable for WLC1115**

# infineon

**About WLC1115**

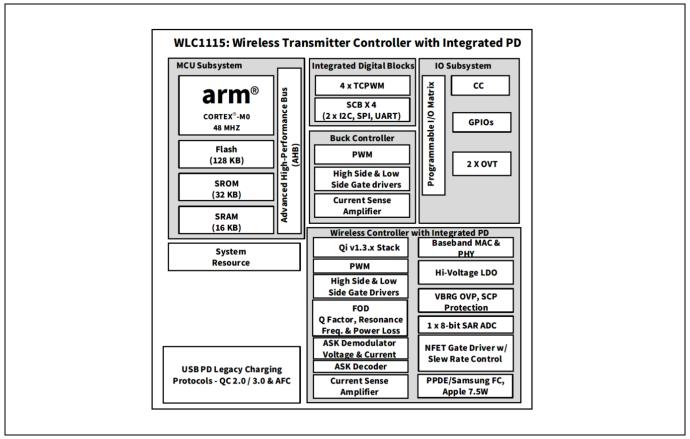

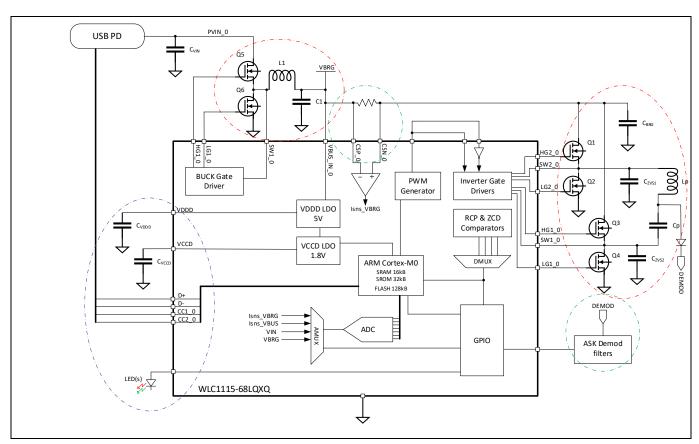

**Figure 1** shows the WLC1115 internal architecture in the form of a logic block diagram. Refer to the datasheet [2] for more details.

Figure 1 WLC1115 logic block diagram

#### 1.2 WLC1115 in wireless transmitter application

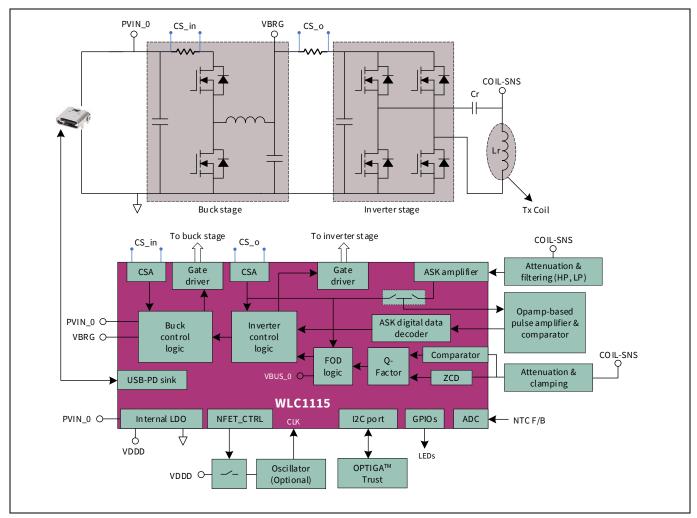

A Qi-compliant wireless power transmitter unit with WLC1115 is shown in **Figure 2** for the MP-A11 coil. A Qi-certified transmitter seamlessly works with a Qi-certified receiver irrespective of the make or the Qi Standard used. The most common power supply to the transmitter unit uses a USB-C power adapter through the Type-C connector. The MP-A11 coil-based transmitter system uses fixed-frequency variable-input voltage control for the inverter stage. The variable voltage is provided by the buck stage. With a USB-PD type input, the input voltage can be dynamically changed to keep the buck stage input close to the output, which optimizes the buck stage efficiency.

A transmitter board with WLC1115 needs a minimal number of external components for system control. Some signal conditioning circuits and amplifier circuits are required for the in-band communication. WLC1115 integrates the buck and inverter stage control. All the protection features for buck are also available within WLC1115. An external authentication chip interfaced to WLC1115 over I<sup>2</sup>C completes the requirements for the Qi 1.3.x Standard. The internal oscillator of WLC1115 meets the needs of FSK for in-band communication. For a higher-resolution clock (to have better accuracy for proprietary implementation), an external oscillator can be interfaced with WLC1115.

WLC1115 monitors the individual power stage currents and voltages for implementing the protection features. With an on-chip 32-bit Arm® Cortex®-M0 processor, 128 kB Flash, 16 kB RAM and 32 kB ROM, the firmware supporting the complete Qi state machine logic can be programmed on to WLC1115.

#### Applicable for WLC1115

# infineon

#### **About WLC1115**

Figure 2 Wireless power transmitter system with WLC1115

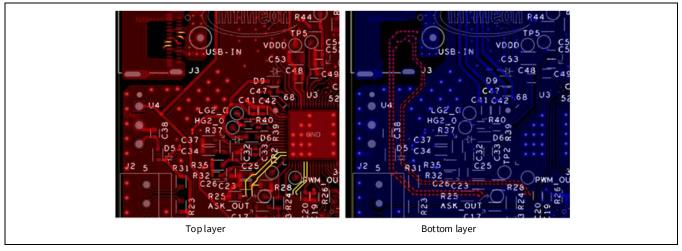

#### 1.3 MP A11 15 W power transmitter board (REF\_WLC\_TX15W\_C1)

REF\_WLC\_TX15W\_C1 MP-A11 15 W transmitter board, based on WLC1115, is a Qi-compliant transmitter design with MP-A11 type transmitter coil. The transmitter unit works with an input from a Type-C USB-PD adaptor. The transmitter board offers the following value propositions:

- Low bill of materials (BOM) cost for Qi v1.3.2 compliance

- Single MCU system that handles USB-PD, buck, inverter control and Qi state machine

- Form factor comparable to off-the-shelf chargers

- Simple to manufacture; ready-to-market layout

- Critical system-level parameters (foreign object detection (FOD) power loss threshold, inverter switching frequency, etc.) are configurable using a utility

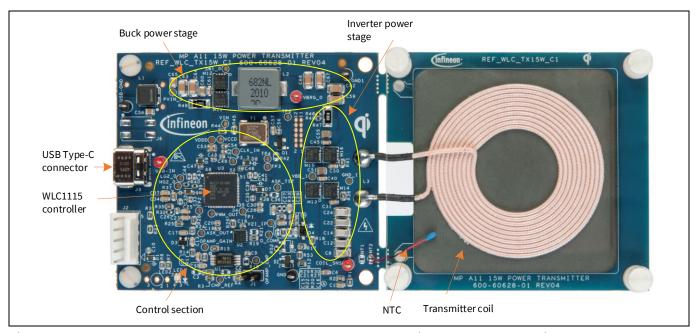

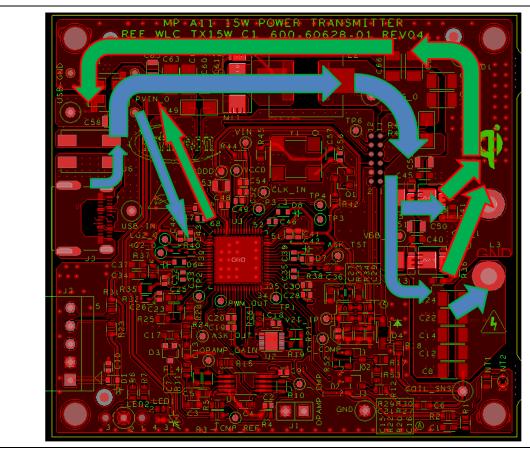

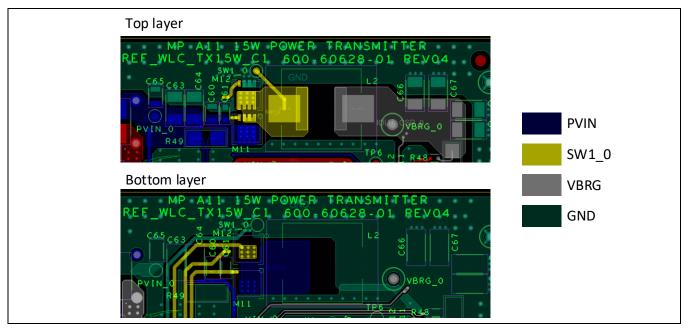

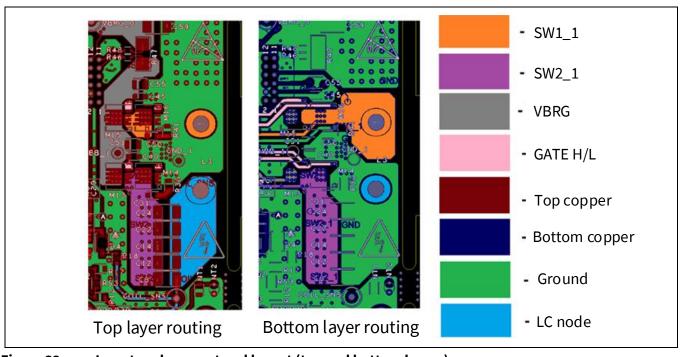

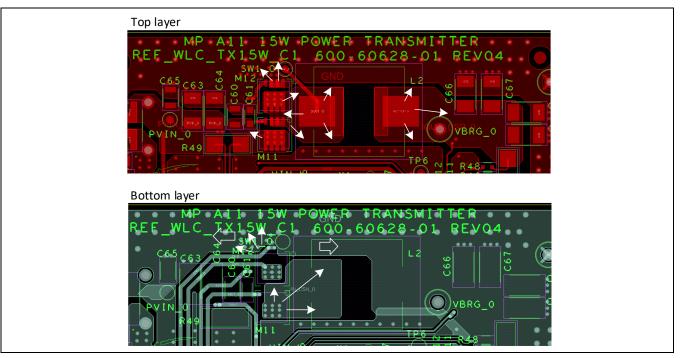

The 15-W transmitter solution board is developed on a compact two-layer PCB. The PCB area under the MP-A11 transmitter coil is just FR4 without any copper. This is for a mechanically secure interface and for connecting the Tx coil to the PCB circuitry, and this part of the board can be cut. The board top-side placement section with key sections is shown in **Figure 3**. The wireless charger transmitter board key specifications are listed in **Table 1**.

#### **Applicable for WLC1115**

#### **About WLC1115**

Figure 3 REF\_WLC\_TX15W\_C1 MP-A11 15 W power transmitter board key sections

Table 1 REF\_WLC\_TX15W\_C1 power transmitter board brief specification

| Parameter                                      | Value                                                          |  |  |  |

|------------------------------------------------|----------------------------------------------------------------|--|--|--|

| Feature list                                   |                                                                |  |  |  |

| Compatible transmitter coil                    | 1-coil MP-A11                                                  |  |  |  |

| Input type/Connector                           | USB Type-C                                                     |  |  |  |

| Input PDO voltage                              | 9 V, 15 V, 20 V                                                |  |  |  |

| Typical output power                           | 15 W                                                           |  |  |  |

| Peak system efficiency                         | More than 83 percent with test receiver WRM483265-10F5-12V-G   |  |  |  |

| Inverter switching frequency                   | 127.7 kHz                                                      |  |  |  |

| Standby power                                  | 13.4mA at 5V i.e 67mW                                          |  |  |  |

| ASK demodulator                                | AC voltage (coil voltage) based and DC current based           |  |  |  |

| FSK modulator                                  | Meets Qi v1.3.2 requirements                                   |  |  |  |

| Foreign object detection                       | Based on power loss, Q-factor and resonant frequency           |  |  |  |

| Other Protections                              | OVP, UVP, OCP, short-circuit protection (SCP), OTP             |  |  |  |

| Authentication                                 | Meets Qi v1.3.2 requirements                                   |  |  |  |

| PCB details                                    | 59 x 66 mm/two layers/2 oz. copper                             |  |  |  |

| Operating temperature                          | 0°C to +85°C                                                   |  |  |  |

| Storage temperature                            | -40°C to +125°C                                                |  |  |  |

| Other features                                 | Samsung proprietary extension, up to 7.5W charging for iPhones |  |  |  |

| Compliance / Certification                     |                                                                |  |  |  |

| USB certification                              | USB certification                                              |  |  |  |

| Qi certification                               | Qi certification                                               |  |  |  |

| Conducted and radiated emission pre-compliance | Conducted and radiated emission pre-compliance                 |  |  |  |

infineon

Hardware design

#### 2 Hardware design

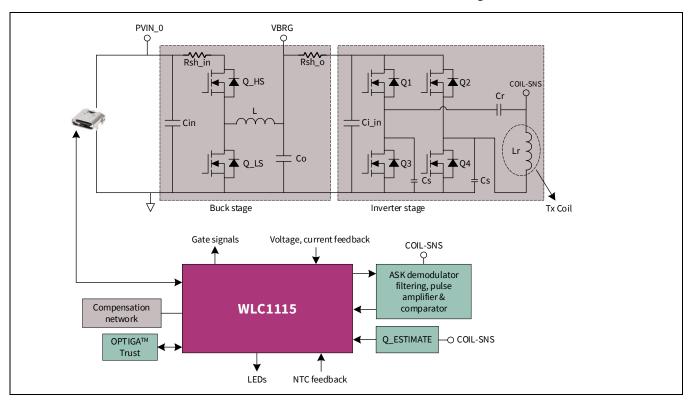

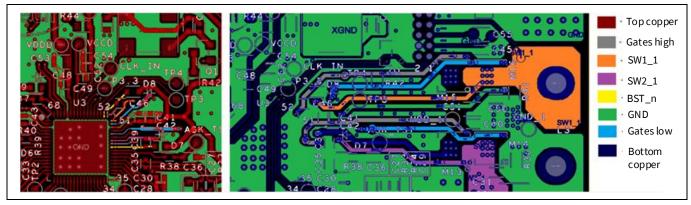

This section covers the requirements and design or selection criteria for the transmitter board key components shown in **Figure 4**. The blocks in gray indicate the power stage components. The blocks in green are the circuit blocks for the control section of the WLC1115-based wireless transmitter design.

Figure 4 WLC1115-based wireless transmitter board key components

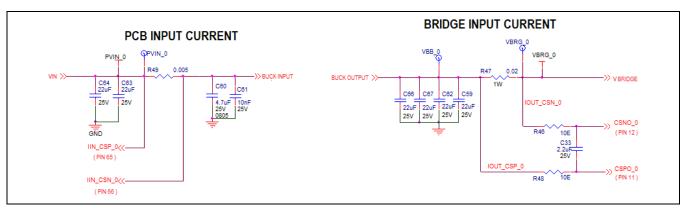

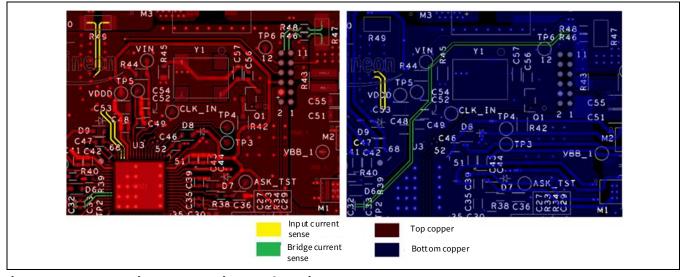

#### 2.1 Buck power stage

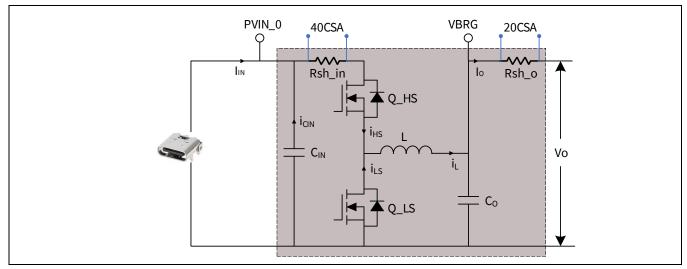

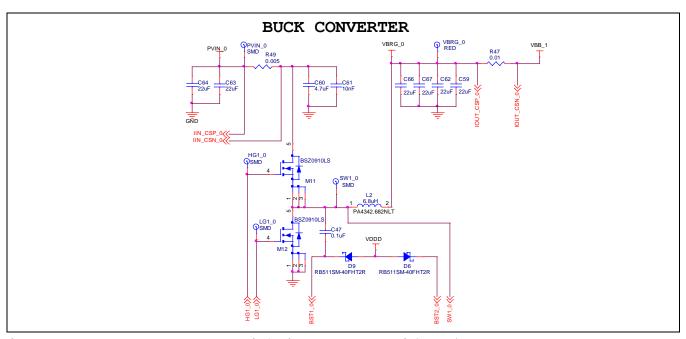

The DC-DC converter stage in REF\_WLC\_TX15W\_C1 is shown in **Figure 5**. The power stage consists of a filter at input, a synchronous buck converter power stage, and shunt resistors for control and output current measurements.

Figure 5 Buck converter stage in REF\_WLC\_TX15W\_C1

#### Hardware design

The input to the buck converter is from a USB-PD source or from a standard AC-DC power adapter with fixed output voltage. With a USB-PD input, the PD contract is adjusted dynamically based on the buck converter output voltage requirement to keep stress on FETs minimal and hence achieve good efficiency. The closed-loop control for the buck stage is based on peak current mode control (PCMC), most of which is implemented inside WLC1115. The external components for control are the Type 2 compensation network components (refer to section **0**). The output voltage and Q\_HS current are used for output voltage regulation. Since the gate drivers, high-side current sense (CS) amplifiers and voltage feedback networks are integrated into WLC1115, the converter stage is highly simplified.

Use of WLC1115 helps in having the following features for the buck stage:

- 1. Highly integrated PD-based solution, compliant with latest USB Type-C PD requirements

- 2. Integrated gate drivers and firmware-configurable turn-on/-off gate drive strength

- 3. Switching frequency range up to 600 kHz

- 4. Flexibility to dynamically change input voltage to 5 V, 9 V, 15 V or 20 V with PD input

- a. Helps achieve good efficiency

- b. Reduces standby power by operating at 5 V in idle mode

- 5. Protections on input and output side of buck stage

- a. Input UVP, OVP

- b. Output UVP, OVP

- c. Output OCP, SCP

- d. Protections specific to PD (e.g., VBUS to CC short)

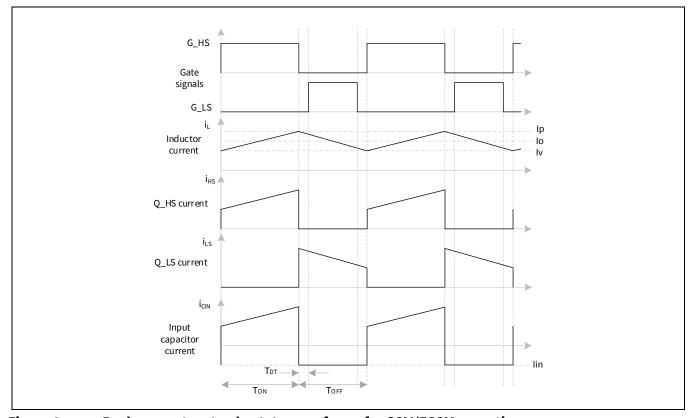

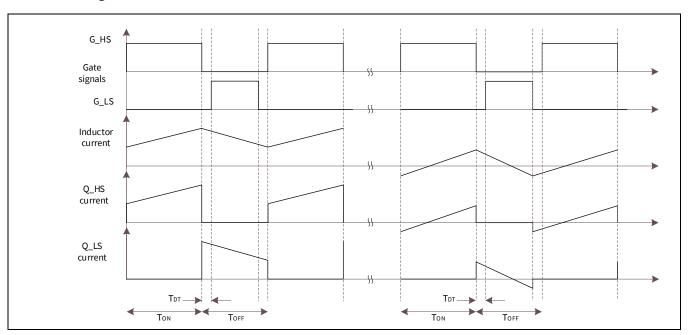

The steady-state waveforms for key components of the buck converter are shown in **Figure 6** for continuous conduction mode (CCM) or forced continuous conduction mode (FCCM) operation. The design and selection of power stage components of the buck stage can be derived from the steady-state waveforms.

Figure 6 Buck converter steady-state waveforms for CCM/FCCM operation

#### **Applicable for WLC1115**

Hardware design

#### 2.1.1 Inductance requirement and selection

The inductance value for the buck power stage is set to keep the converter in CCM at full load. The inductance value is computed as follows:

$$L = \frac{V_{in}D(1-D)}{F_S\Delta i_L}$$

Where:

$V_{in}$  – input voltage

D – buck operating duty cycle

$$D = \frac{T_{ON}}{T_{ON} + T_{OFF}} = T_{ON}F_S = \frac{V_O}{V_{in}}$$

$F_S$  – switching frequency

$\Delta i_L$  is the ripple current in the inductor and is set to around 50 percent to 70 percent of average inductor current  $I_O$ . For high-power applications,  $\Delta i_L$  is set to around 20 percent to 40 percent of  $I_O$ , which is useful for reducing EMI levels and current stress on FETs and filter capacitors.

From the inductance equation, the ripple current is at the maximum when the duty cycle is 0.5.

**Inductor RMS current** – The inductor current contains ripple content on a DC current. The inductor RMS current for design/selection and loss estimations is calculated as:

$$I_{Lrms} = \sqrt{{I_0}^2 + \left(\frac{\Delta i_L}{2\sqrt{3}}\right)^2}$$

Where  $I_0$  is the average output current and is the same as the average inductor current.

**Inductor peak current** – The peak current rating without saturation is based on full load current for 150 percent load (short-term overload expected for a few seconds) and ripple current for the same operating conditions.

$$I_{Lpk} = (1.5 \times I_O) + \frac{\Delta i_L}{2}$$

**Inductor losses** – The inductor has a copper loss and a core loss component. The copper loss arises from the DC resistance of the inductor. The AC resistance due to ripple is ignored.

$$P_{Lcu} = I_{Lrms}^{2} R_{Ldc}$$

The ripple current and associated magnetic flux swing in the inductor core contribute to core losses. The core loss data as a function of flux swing  $\Delta B$  and frequency is given by the manufacturer:

$$P_{Lcore} = CF_S^{\alpha} \Delta B^{\beta} V_e$$

Where the constants C,  $\alpha$  and  $\beta$  are specified by the manufacturer,  $V_e$  is the core material volume. Alternatively, the manufacturer provides tools for easy computation of losses in the inductor.

**Inductor selection guidelines** – The selected inductor part should meet the following requirements:

- 1. Inductance value to satisfy the ripple current requirements for the entire operating range

- 2. Current rating greater than  $I_{Lrms}$  and  $I_{Lpk}$

- 3. Low DCR for low conduction loss and thermal rise

- 4. Core material with low core loss at 400 kHz

- 5. Shielded construction for low radiated emissions

- 6. SMD type mounting

#### **Applicable for WLC1115**

Hardware design

#### **Buck stage input capacitor** 2.1.2

As shown, when the high-side MOSFET is turned on, the MOSFET current is pulsating with peak current equal to the inductor peak current. This pulsating current has higher magnitude than the average input current, causing larger voltage ripple and higher EMI.

Input filter capacitors, placed close to the FETs, provide a low-impedance path for pulsating currents, and clean current is drawn from the source. When Q\_HS is turned on, the capacitor current is the difference between input current  $I_{IN}$  and inductor current  $i_L(t)$ . The capacitor discharges in this state and, along with  $I_{IN}$ , provides energy to load. When Q\_HS is turned off, the input capacitor is charged with a current equal to  $I_{IN}$ . As the capacitor charges, there is a ripple  $\Delta V_{in}$  across capacitor and the magnitude of ripple is dependent on capacitance value and the ESR of the capacitor.

$$I_{IN} = C_{IN} \frac{d V_{in}}{dt} = C_{IN} \frac{\Delta V_{in}}{T_{OFF}}$$

$$C_{IN} > \frac{I_{IN}(1-D)}{\Delta V_{in} F_S}$$

Where  $I_{IN}$  is the input current:

$\Delta V_{in}$  is the ripple voltage allowed in input (recommended to be set at less than 3 percent of  $V_{in}$ ).

The input capacitor RMS current, derived from the waveform in Figure 6, is:

$$I_{CIN_{rms}} = \sqrt{\frac{1}{T_S} \int_0^{T_S} i_{CIN}(t)^2 dt}$$

$$I_{CIN_{rms}} = \sqrt{\frac{1}{T_S}} \int_0^{DT_S} (i_L(t) - I_{IN})^2 dt + \int_{DT_S}^{T_S} I_{IN}^2 dt$$

$$I_{CIN_{rms}} = \sqrt{\frac{1}{T_S}} \int_{0}^{DT_S} \left( I_O - \frac{\Delta i_L}{2} + \frac{\Delta i_L t}{D T_S} - I_{IN} \right)^2 dt + \int_{DT_S}^{T_S} I_{IN}^2 dt$$

$$I_{CIN_{rms}} = \sqrt{D\left(I_0^2(1-D) + \frac{\Delta i_L^2}{12}\right)}$$

Power loss in capacitor – The power loss in the input capacitor is due to the capacitor ESR and the associated ripple current in it.

$$P_{Cin} = \frac{{I_{CIN_{rms}}}^2 R_C}{N_{cap}}$$

Where

$R_C$  – ESR of capacitor part selected

$N_{cap}$  – number of capacitors connected in parallel

The formula is valid under the assumption that the capacitors are identical in value and electrical properties.

#### **Applicable for WLC1115**

#### **Capacitor selection guidelines**

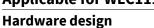

1. **Capacitor voltage rating** – The capacitor should be rated for the withstanding voltage in **Table 1**. Ceramic capacitors, most suitable for low-voltage DC input, are available with X5R, X6R or X7R dielectric and have a range of capacitance values with applied voltage.

**Figure 7** (a) shows capacitance vs. DC bias for a CL31X226KAHN3NE (22  $\mu$ F 25 V rated) capacitor. At 20 V, the capacitance drops down to 4  $\mu$ F (82 percent dip). The capacitor bank should be sized based on this bias characteristic. The number of capacitors in parallel should ensure that the effective capacitance value is greater than or equal to  $C_{IN}$  for the particular operating input voltage.

Figure 7 CL31X226KAHN3NE characteristics

2. **Capacitor ESR** –  $C_{IN}$  effective capacitance calculated value only deals with the voltage ripple caused by the discontinuous capacitor current inherent in the switching behavior of the buck regulator. There will be additional voltage ripple caused by the  $C_{IN}$  ESR and the buck input capacitor switching current ripple; therefore, the additional input voltage ripple resulting from the current through the input capacitors can be calculated by the following equation:

$$\Delta V_{in} = \frac{I_{IN}(1-D)}{C_{IN} F_S} + I_{IN} R_{C_{IN}}$$

The ESR-induced ripple should keep the overall ripple voltage below the desired  $\Delta V_{in}$ . Paralleling of capacitors will reduce the effective  $R_{C_{IN}}$  and hence the ESR induced ripple.

3. Capacitor ripple current rating – The ripple current, along with capacitor ESR, results in temperature rise inside the capacitor. Temperature rise with RMS ripple current is shown in Figure 7 (b) for CL31X226KAHN3NE. The temperature rise at the highest operating ambient should keep the capacitor temperature below its rated operating limits. Paralleling capacitors will divide the current and hence reduce the thermal stress on individual capacitors.

#### 2.1.3 Buck stage output capacitor

The output capacitor is essential to keep the switching voltage ripple within a specified limit and to cater for load-transient response. The feedback control loop adjusts the output voltage for any load transients, but when load step/dump rate is faster than loop response time, the output capacitor has to ensure that output undershoot/overshoot is contained within the specified value.

#### Hardware design

To maintain the voltage ripple at switching frequency below a specified value ( $\Delta V_O$  – typically less than 5 percent of output voltage), the minimum output capacitance required is:

$$C_{O1} = \frac{\Delta i_L}{8 F_S \Delta V_O}$$

Output capacitance to meet the transient requirements is:

$$C_{O2} = \frac{I_{O_{Step}}}{V_{Odin}} \frac{1}{2\pi F_{BW}}$$

Where:

$I_{O_{Step}}$  is the load current step (worst case is 150 percent of full load current)

$V_{Odip}$  is the allowed dip in output voltage for the load step

$F_{BW}$  is the control loop bandwidth, which is set at less than 1/10 of the switching frequency

The output capacitance required is a maximum of  $C_{O1}$  and  $C_{O2}$ . The ripple current through the capacitor is the ripple content of inductor current. The RMS capacitor current is:

$$I_{CO_{rms}} = \frac{\Delta i_L}{2\sqrt{3}}$$

The loss in output capacitors is:

$$P_{Co} = \frac{{I_{CO_{rms}}}^2 R_C}{N_{cap}}$$

The capacitor part selection and bank sizing criteria are based on capacitance change with bias and temperature rise due to ripple current (as applicable for an input capacitor).

#### 2.1.4 Power MOSFET selection for buck stage

The MOSFET selection depends on the worst-case operating conditions the converter operates at. The voltage rating should be at least 1.5 times the maximum operating voltage or slightly higher than peak withstanding voltage, whichever is higher. The peak current in the MOSFET is the same as the peak inductor current. The MOSFET current rating at the highest case temperature should be greater than the computed peak current.

$$V_{ds-pk} = \max\left(\left(1.5V_{in-op}\right), V_{in-withstand}\right)$$

$$I_{ds-pk} = I_{Lpk} = (1.5 \times I_O) + \left(\frac{\Delta i_L}{2}\right)$$

Power loss is another key parameter for MOSFET part selection. The MOSFET characteristics such as on-state resistance, switching transition times, gate charge, package area, thermal impedance, etc. govern the MOSFET part selection.

#### **Applicable for WLC1115**

Hardware design

#### 2.1.4.1 Conduction loss

The current through the FETs is pulsating, as shown in **Figure 6.** The RMS current of the high-side or main MOSFET is derived from the current waveform as:

$$I_{Qrms_{HS}} = \sqrt{\frac{1}{T_S} \int_0^{T_S} i_{Q_{HS}}(t)^2 dt}$$

$$I_{Qrms_{HS}} = \sqrt{\frac{1}{T_S} \int_0^{DT_S} \left( I_O - \frac{\Delta i_L}{2} + \frac{\Delta i_L t}{D T_S} \right)^2 dt}$$

$$I_{Qrms_{HS}} = \sqrt{D\left(I_O^2 + \frac{\Delta i_L^2}{12}\right)}$$

When Q\_HS is turned off, the inductor current freewheels through the diode of Q\_LS. Synchronous rectification (SR) MOSFET Q\_LS is turned on to give a low impedance path for freewheeling current and hence reduce conduction losses. The SR MOSFET RMS current is computed as:

$$I_{Qrms_{LS}} = \sqrt{\frac{1}{T_S} \int_0^{T_S} i_{Q_{LS}}(t)^2 dt}$$

$$I_{Qrms_{LS}} = \sqrt{\frac{1}{T_S} \int_0^{(1-D)T_S} \left( I_O + \frac{\Delta i_L}{2} + \frac{\Delta i_L (t - DT_S)}{(D-1)T_S} \right)^2 dt}$$

$$I_{Qrms_{LS}} = \sqrt{(1-D)\left(I_0^2 + \frac{\Delta i_L^2}{12}\right)}$$

The conduction loss in the MOSFET occurs due to the on-state resistance  $R_{ds(on)_{HS}}$  and  $R_{ds(on)_{LS}}$ . This resistance is a function of temperature, and the value at the highest operating temperature from the datasheet should be considered for the worst-case scenario. The conduction loss in FETs is computed as:

$$P_{C-Q_{HS}} = I_{Qrms_{HS}}^2 R_{ds(on)_{HS}}$$

$$P_{C-Q_{LS}} = I_{Qrms_{HS}}^{2} R_{ds(on)_{LS}}$$

#### 2.1.4.2 Dead time loss

A dead band is provided between the gate signals of high-side and low-side FETs, as in **Figure 6**. This dead band ensures that there is no cross-conduction between FETs, causing short of input supply. Also, when Q\_HS is turned off, the energy in the inductor will discharge the  $C_{oss}$  of Q\_LS and start body diode conduction of Q\_LS within this dead band before the gate signal is applied. The conduction loss occurring in the body diode is:

$$P_{TD} = F_S V_F \left( \left( I_O + \frac{\Delta i_L}{2} \right) T_{DT1} + \left( I_O - \frac{\Delta i_L}{2} \right) T_{DT2} \right)$$

Where:

$V_F$  is the forward drop of body diode of the MOSFET.

$T_{DT1}$  and  $T_{DT2}$  are the dead time at turn-off and turn-on of the Q\_HS gate, respectively. If the dead times are set as identical at  $T_{DT}$ , then the dead time loss is:

$$P_{TD} = F_S V_F T_{DT} (2I_O)$$

#### **Applicable for WLC1115**

Hardware design

#### 2.1.4.3 Switching losses

#### **High-side MOSFET switching losses**

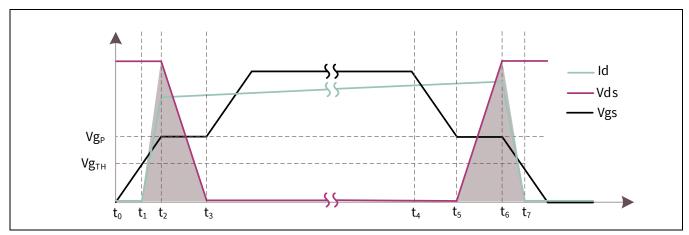

The high-side MOSFET has switching losses when the gate is toggled. The losses are dependent on the MOSFET parasitic capacitances and the gate resistance. **Figure 8** shows typical MOSFET switching characteristics, and the region where switching losses occur are shaded in gray.

Figure 8 MOSFET turn-on and turn-off characteristics

The MOSFET turn-on loss is the shaded area between  $t_1$  and  $t_3$ , and is given by:

$$\begin{split} P_{SW-ON} &= \frac{1}{2} V_{IN} \left( I_O - \frac{\Delta i_L}{2} \right) t_{ON} \\ t_{ON} &= (t_2 - t_1) + (t_3 - t_2) \\ t_{ON} &= \left( R_{GON} C_{iss} \ln \left( \frac{V_{dr} - V_{gth}}{V_{dr} - V_{an}} \right) \right) + \left( \frac{R_{GON}}{V_{dr} - V_{an}} V_{IN} C_{rss} \right) \end{split}$$

Where:

$R_{GON}$  is the gate resistance for rising gate voltage (sum of MOSFET internal gate resistance, driver pull-up and external gate resistor)

$C_{iss}$  and  $C_{rss}$  are MOSFET parasitic capacitors specified in the datasheet

$V_{dr}$  is the gate driver supply voltage

$V_{gth}$  and  $V_{gp}$  are MOSFET gate threshold and gate plateau voltage specified in the datasheet.

Similarly, the MOSFET turn-off loss is the shaded area between  $t_7$  and  $t_5$ , and is given by:

$$\begin{split} P_{SW-OFF} &= \frac{1}{2} V_{IN} \left( I_O + \frac{\Delta i_L}{2} \right) t_{OFF} \\ t_{OFF} &= \left( t_6 - t_5 \right) + \left( t_7 - t_6 \right) \\ t_{OFF} &= \left( R_{GOFF} C_{iss} \frac{V_{gp}}{V_{ath}} \right) + \left( \frac{R_{GOFF}}{V_{gp}} V_{IN} C_{rss} \right) \end{split}$$

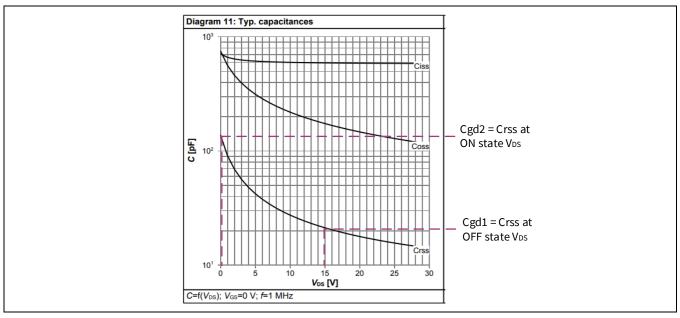

In the switching loss equations, the  $V_{DS}$  rise and fall is assumed to be linear and constant  $C_{rss}$ , which is non-ideal as shown in **Figure 9** for BSZ0910ND, and it is difficult to incorporate the non-linearity in computations.

# infineon

#### Hardware design

One method to include non-linearity is to take the average of  $C_{rss}$  at turn-on and turn-off voltage [4].

$$C_{rss} = \frac{Cgd2 + Cgd1}{2} = \frac{C_{rss}@0V + C_{rss}@V_{IN}}{2}$$

Figure 9 C<sub>rss</sub> variation with V<sub>DS</sub> and identifying Cgd1 and Cgd2

#### **Reverse recovery losses**

When the high-side MOSFET turns on, the reverse recovery phenomenon is seen in the body diode of the low-side MOSFET. The reverse recovery loss of the bottom-side MOSFET will occur in the high-side MOSFET and adds to the turn-on losses.

$$P_{DRR} = Q_{rr}V_{IN}F_{S}$$

Where  $Q_{rr}$  is the reverse recovery charge of the body diode of Q\_LS and is provided in the datasheet.  $Q_{rr}$  is also a function of diode forward current and the current slope in the diode during turn-off [5].

#### Other switching losses

Furthermore, the high-side MOSFET output capacitance must be charged during switching, and the associated loss is:

$$P_{COSS} = \frac{1}{2} C_{oss} V_{IN}^2 F_S = \frac{1}{2} Q_{oss} V_{IN} F_S$$

Where:

$C_{oss}$  is the MOSFET output capacitance provided in the datasheet. Some manufacturers also provide the information as output charge  $Q_{oss}$ .

The steady-state MOSFET currents for a buck converter operating in FCCM are shown in **Figure 10** for full-load and light-load conditions. When the inductor valley current is positive, which is typically case for inductance design for CCM, the high-side MOSFET will have a hard turn-on and turn-off switching. For FCCM operation at light loads, the Q\_HS body diode conducts when Q\_LS is turned off, and so turn-on of Q\_HS is with zero voltage switching (ZVS). Also, when Q\_LS is turned off, the current in Q\_LS body diode is not interrupted and so there is no recovery loss.

### Infineo

#### Hardware design

Figure 10 MOSFET currents in FCCM operation: (a) full load; (b) light load

#### **Low-side MOSFET switching losses**

As shown in **Figure 10**, the inductor current is always positive when Q\_HS is turned off, which will forward bias the body diode of Q\_LS before the gate of Q\_LS is applied. Thus, Q\_LS always turns on with ZVS. For CCM operation at full load, the Q\_LS gate pulse is removed but the drain source voltage is still tied to the forward drop voltage of the body diode, resulting in nearly zero turn-off loss as well. There will be reverse recovery-related losses associated with Q\_LS turn-off, but since the reverse current will be supplied by Q\_HS, the corresponding losses appear in Q\_HS in the form of higher turn-on losses.

When inductor valley current is negative, at light load or in the case of a large ripple, Q\_LS will turn on with ZVS, but turn-off is hard with a loss:

$$P_{D-OFF} = \frac{1}{2} V_{IN} \left| I_O - \frac{\Delta i_L}{2} \right| t_{OFF}$$

#### 2.1.4.4 Gate drive power

The gate charging and discharging consumes a certain amount of power, which is supplied from the gate driver supply. The gate power is a function of total gate charge and switching frequency:

$$P_{GATE} = Q_G V_{dr} F_S$$

Where:

$V_{dr}$  is the driver supply voltage

$Q_G$  is the gate charge.

The value is available in the datasheet and must be selected for  $V_{dr}$  level.

#### MOSFET selection guidelines for buck stage

- 1. The selected part should be rated for  $V_{ds-pk}$  and  $I_{ds-pk}$  over the entire operating temperature range specified in the datasheet.

- 2. Select a part with low  $R_{DS(on)}$  for lower conduction losses. For FCCM operation, there will be circulating current at light load, and low  $R_{DS(on)}$  helps in reducing light power losses.

# infineon

#### Hardware design

- 3. For Q\_HS, low  $C_{rss}$  and  $C_{oss}$  parts will give low switching losses. For Q\_LS, select the part whose body diode has low reverse recovery charge, preferably less than 5 nC.

- 4. The integrated gate drivers in WLC1115 drive the MOSFET gate with 5 V. The selected MOSFET part should be logic-level driven (should have the specified R<sub>DS(on)</sub> at gate voltage of 4.5 V).

- 5. WLC1115 has integrated gate resistance, the value of which can be firmware-configured to up to 33  $\Omega$ , and internal pull-down resistors. There is no need for external gate resistors.

- 6. MOSFETs with SMD package are preferred. Avoid using a through-hole part because the lead inductance will add to switching losses and emissions.

- 7. The MOSFET package should be such that the thermal management is manageable with natural cooling, without occupying much PCB area. Refer to section **4.4** for thermal management for MOSFETs.

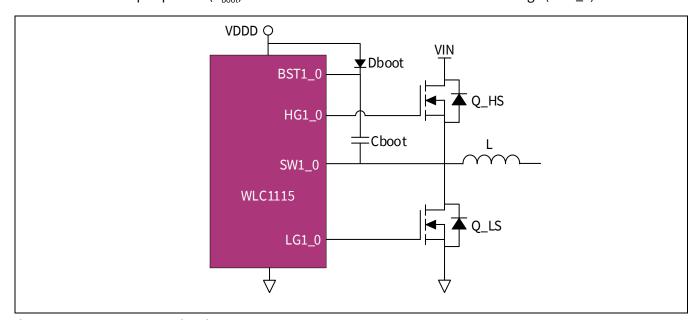

#### 2.1.5 Bootstrap circuit

The buck stage FETs are driven using inbuilt gate drivers of WLC1115. The high-side MOSFET requires a voltage supply referenced at the switching node or source of Q\_HS. A bootstrap circuit built using  $C_{boot}$  and  $D_{boot}$  is used (refer to **Figure 11**) to generate the supply for Q\_HS.

The  $C_{boot}$  must be able to supply a charge (= 2\*gate charge) and retain its full voltage. If that does not happen, there will be a significant amount of ripple on the Q\_HS gate drive supply.

$C_{boot} \gg 20C_a$

$$C_g = \frac{Q_g}{\text{VDDD} - V_{F-Dhoot}}$$

$VDDD = V_{dr}$  is the supply voltage and is the same as the Q\_LS gate drive supply.

$Q_g$  is the gate charge of the MOSFET.

$V_{F-Dhoot}$  is the forward drop of bootstrap diode  $D_{hoot}$ .

The chosen bootstrap capacitor ( $C_{boot}$ ) should be able to withstand switch node voltage (SW1\_0) + VDDD.

Figure 11 Bootstrap circuit

#### Hardware design

The bootstrap diode  $(D_{boot})$  needs to be able to block the full-power rail voltage, which is seen when the high-side MOSFET (S1) is switched on. It must be a fast recovery diode to minimize the amount of charge fed back from the bootstrap capacitor  $(C_{boot})$  into the VDDD supply, and similarly the high temperature reverse leakage current will be important if the capacitor must store charge for long periods of time. The current rating of the bootstrap diode is the average gate current:

$$I_{Dboot} = \frac{P_{GATE}}{\text{VDDD}} = Q_G F_S$$

#### 2.1.6 Current sense resistor selection

WLC1115 uses internal high-side current sense amplifiers (CSAs) for input current and load current. The input current feedback is mainly for PCMC and is not the same as the DC input current. The output current feedback in wireless charging is used for inverter power measurement for power loss calibration and FOD. The value of the external CS resistors is critical to the control of the buck converter and reliable FOD.

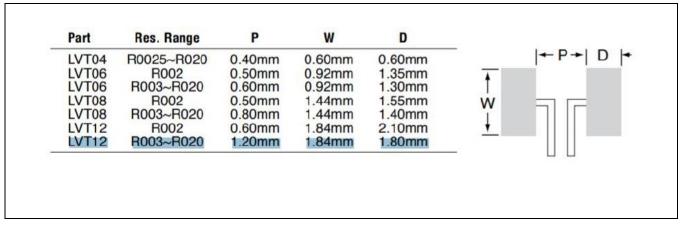

For the input CS resistor  $R_{sh_{in}}$ , WLC1115 requires a 5 m $\Omega$  CS resistor. For output CS resistor  $R_{sh_o}$ , WLC1115 requires a 10 m $\Omega$  CS resistor for a good sensing range and ADC resolution.

#### Sense resistor part selection

Sense resistor losses and ease of routing determine the selection of the resistor package. The resistor losses are:

$$\begin{split} P_{Rsh_{in}} &= I_{Rsh_{in}}^{2} R_{sh_{in}} \\ I_{Rsh_{in}} &= I_{Qrms_{HS}} \\ P_{Rsh_{o}} &= I_{Rsh_{o}}^{2} R_{sh_{o}} \\ I_{Rsh_{o}} &= I_{O} \end{split}$$

For a 15 W design, the losses are 0.02 W and 0.06 W in input and output shunt resistors, respectively. Going by loss numbers, a resistor package of 0603 would be sufficient. But the feedback traces from the sense resistor should be taken as shown on the right-hand side of **Figure 12**. Considering the routing guidelines in **Table 9** and associated creepage requirements between traces and pads, the 1206 package is most suitable for CS resistors.

Figure 12 Typical SMD resistor packages and land patterns

#### **Applicable for WLC1115**

Hardware design

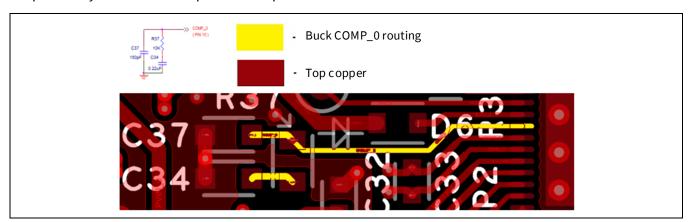

#### 2.1.7 Type 2 compensator for buck stage

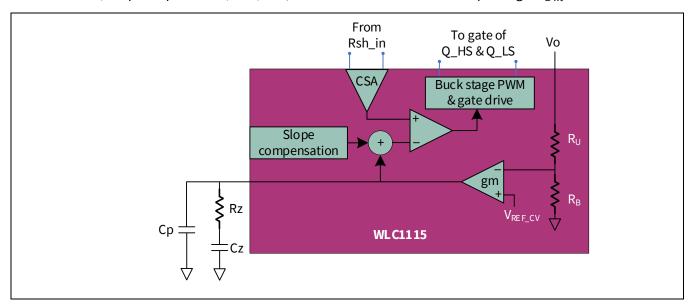

For the MP-A11 coil-based wireless transmitter, WPC recommends control of DC voltage to inverter bridge to regulate the power delivered to receiver. The buck stage constant voltage (CV) feedback loop with an external compensation network regulates the buck output voltage with 20 mV step size for reference. The control-loop architecture for the buck stage is shown in **Figure 13**.

WLC1115 incorporates PCMC for the buck stage, using the output voltage and high-side MOSFET current feedback for CV mode operation. Slope compensation for PCMC is built into WLC1115 along with high-side CSAs and a voltage feedback network. A Type 2 compensation network for the loop is set using external components Rz, Cz and Cp. The choice of external compensation network components is based on cross-over frequency of control-loop bandwidth  $F_{BW}$ , buck converter plant transfer function (dependent on power stage components like inductance, output capacitance, ESR, etc.) and the transconductance amplifier gain  $g_m$ .

Figure 13 Control-loop architecture for buck stage

The plant transfer function for PCMC of the buck converter is given by:

$$G_{VC}(s) = \frac{k R_O}{R_i} \frac{(1 + sR_{CO}C_O)}{(1 + sR_OC_Ok)} F_n(s)$$

$$k = \frac{1}{1 + \frac{T_SR_O}{L} (m_C(1 - D) - 0.5)}$$

$$m_C = 1 + \frac{S_e}{S_n}$$

$$F_n(s) = \frac{1}{1 + \left(\frac{s}{\omega_n}\right)^2 + \frac{s}{O\omega_n}}; \quad \omega_n = \pi F_S$$

Where:

$R_O$  is the load resistance  $(V_O/I_O)$

$R_i$  is the CS feedback gain – the product of shunt resistance value and CSA gain

$R_{CO}$  is the equivalent ESR of the output capacitor

$S_e$  is the external slope added for slope compensation (50 percent to 100 percent of  $\frac{V_O}{L}$ )

# infineon

#### Hardware design

$S_n$  is the input slope of the inductor current

The feedback network gain is:

$$G_{div}(s) = \frac{R_B}{R_B + R_U}$$

Where  $R_B=34.5~k\Omega$  and  $R_U=200~k\Omega$  are the voltage feedback network divider resistors built into WLC1115.

The compensation networks transfer function is:

$$G_{EA}(s) = \frac{1}{sC_Z} \frac{(1 + sR_ZC_Z)}{(1 + sR_ZC_P)}$$

For the compensation network:

- 1. The crossover frequency  $F_{BW}$  is usually set at 1/10 of the switching frequency as a good balance between feedback noise and transient response.

- 2. The compensator zero is placed at the plant dominant pole.

- 3. The compensator pole is set to cancel the plant zero formed by the output capacitor and its ESR. The compensation network components are:

$$R_Z = \frac{2\pi (R_U + R_B) R_i C_O F_{BW}}{R_B g_m}$$

$$C_Z = \frac{R_O C_O}{R_Z}$$

$$C_P = \frac{R_{CO}C_O}{R_Z}$$

The open-loop transfer function of the converter with compensation is:

$$H_{OL}(s) = G_{VC}(s) G_{EA}(s) G_{div}(s)$$

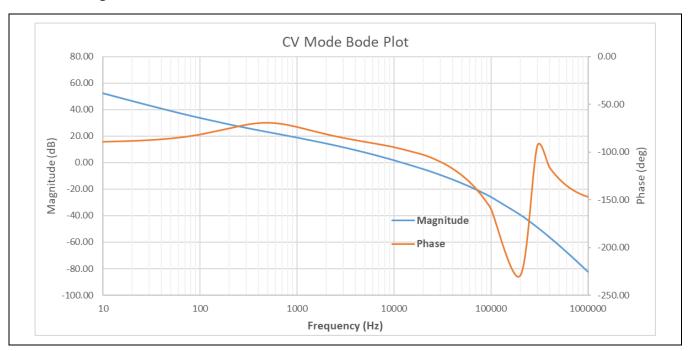

The stability margins are evaluated by plotting the frequency response of the transfer function and determining the gain margin and phase margin. The frequency response for the 15 V input and the 9 V output at 15 W is shown in **Figure 14**, or the buck converter in REF\_WLC\_TX15W\_C1. As the buck converter will operate for a large range of input and output voltages, stability at all operating points should be ensured.

#### Hardware design

Figure 14 Stability plot for 15 V input, 9 V output and 15 W load in REF\_WLC\_TX15W\_C1

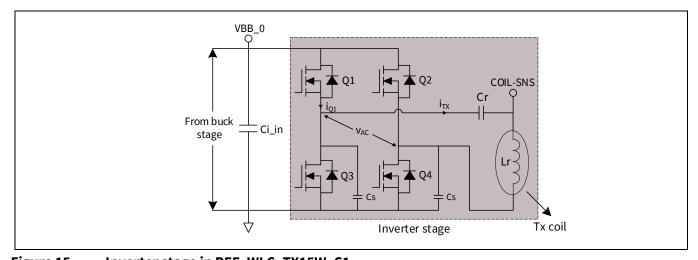

#### 2.2 Inverter power stage

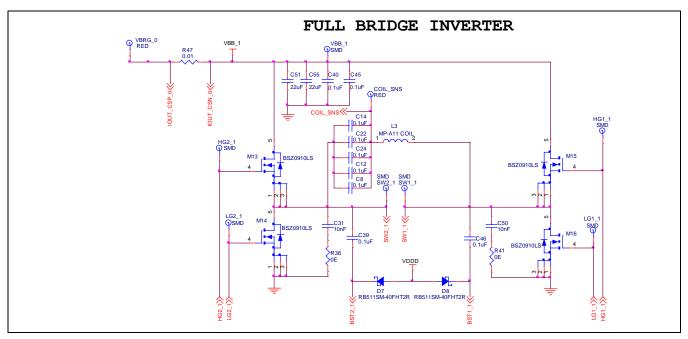

The inverter stage in REF\_WLC\_TX15W\_C1 is shown in **Figure 15**. The power stage consists of a filter capacitor at input, and a full-bridge inverter power stage feeding a resonant tank made up of transmitter coil and resonant capacitor. The input to the inverter is from the buck stage output after the buck output shunt resistor. The four MOSFETs form a full-bridge inverter as recommended for the MP-A11 coil. The snubber capacitors C<sub>s</sub> on each switching node aid in reducing dV/dt during MOSFET turn-on/-off. With proper tuning of snubber capacitor and dead-time, the ZVS turn-on of FETs with minimal body diode conduction can be achieved.

Figure 15 Inverter stage in REF\_WLC\_TX15W\_C1

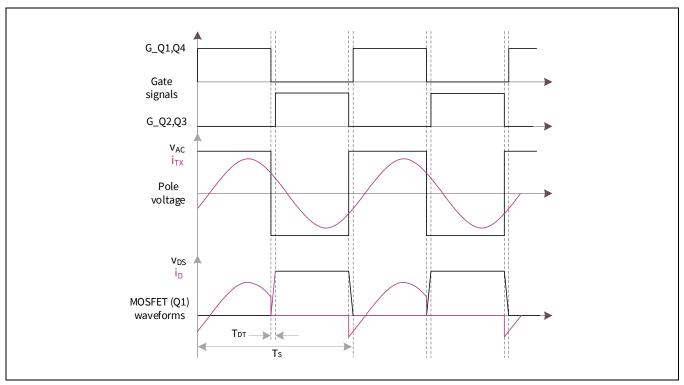

The steady-state waveforms for the inverter stage are shown in **Figure 16**. The waveforms represent the converter state in normal operating range, i.e., after the resonant peak in frequency characteristics. The impedance seen by the bridge is inductive and so the tank current  $i_{TX}$  is lagging behind the tank voltage V AC.

### Applicable for WLC1115

# infineon

#### Hardware design

Figure 16 Inverter steady-state waveforms

#### 2.2.1 Transmitter coil selection

The transmitter coil parameters (inductance, ferrite shield construction) for the MP-A11 coil are from the Qi specifications. The parameters for the MP-A11 coil from [1] are summarized in Table 2.

Table 2 MP-A11 transmitter coil parameters

| Parameter                                      | Value   | Tolerance    |

|------------------------------------------------|---------|--------------|

| Self-inductance                                | 6.3 μΗ  | ± 10 percent |

| Coil outer diameter                            | 44 mm   | ± 1.5 mm     |

| Coil inner diameter                            | 20.5 mm | ± 0.5 mm     |

| Number of turns                                | 10      | _            |

| Number of layers                               | 1 or 2  | -            |

| Ferrite shield thickness                       | 0.5 mm  | _            |

| Coil to shield minimum gap                     | 1 mm    | _            |

| Coil top surface to interface surface gap (dz) | 3.5 mm  | ± 1 mm       |

| Shield extension beyond coil                   | 2 mm    | -            |

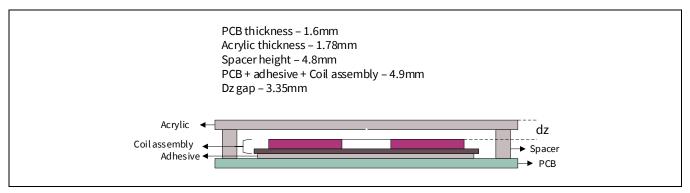

While most of the parameters of the transmitter coil are already taken care of by the manufacturer, the dz gap must be set using the right combinations of spacers and acrylic. The coil assembly used in REF\_WLC\_TX15W\_C1 is shown in **Figure 17**. The coil assembly is mounted on the coil PCB using double-sided tape. The interface surface is an acrylic sheet, and the gap between the sheet and coil is set using four nylon spacers. The spacer height is selected so that the dz gap is close to the Qi-recommended nominal value.

#### **Applicable for WLC1115**

#### Hardware design

Figure 17 MP-A11 coil assembly and associated measurements in REF\_WLC\_TX15W\_C1

#### **Transmitter coil losses**

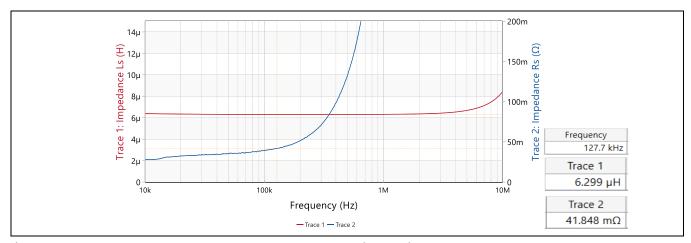

The coil losses consist of conduction losses in windings and core losses in the ferrite shield. For conduction losses, the coil resistance, both DC resistance and skin-effect induced AC resistance, come into the picture. To precisely predict conduction losses, use the Q factor curve provided by the manufacturer and compute the total resistance at the operating frequency. Alternatively, use an impedance analyzer to obtain the total coil resistance at operating frequency (**Figure 18**).

$$\begin{aligned} P_{coil-cond} &= I_{TXrms}^{2} R_{total} \\ R_{total} &= \frac{Q_{Fs-inv}}{2\pi F_{Sinv} L_{tx}} \end{aligned}$$

where  $I_{TXrms}$  is coil RMS current and  $R_{total}$  is the sum of AC and DC resistance of the coil.

Figure 18 Impedance measurements on MP-A11 coil used in REF\_WLC\_TX15W\_C1

Qi recommends use of a Ni-Zn or Mn-Zn ferrite core for shielding of the coil. The ferrite core will have alternating magnetization, resulting in core losses. The core loss computation is similar to that of the buck inductor:

$$\begin{split} P_{Core} &= C F_{S-inv}{}^{\alpha} B_{pk}{}^{\beta} V_{e} \\ B_{pk} &= \frac{L_{r} I_{TXpk}}{N A_{C}} \end{split}$$

Where the constants C,  $\alpha$  and  $\beta$  are specified by the manufacturer:

$V_e$  is the core material volume

$B_{pk}$  is the peak flux in the core

$A_C$  is the core cross-section area (product of the ferrite width and thickness).

#### **Applicable for WLC1115**

# infineon

#### Hardware design

#### Transmitter coil part selection guidelines

- 1. The selected part should match the Qi requirements for the MP-A11 coil (electrical design, ferrite shield design, etc.).

- 2. Inductance value tolerance should not be more than ±10 percent.

- 3. A high Q-factor coil (low total resistance for the 120 kHz to 130 kHz range) is favorable for low losses.

#### 2.2.2 Resonant capacitor selection

The Qi-recommended resonant capacitor value to be used with the MP-A11 coil is 500 nF ±5 percent. As the capacitance value should not vary throughout the operating frequency and voltage range, a capacitor with C0G-type dielectric should be used. Another criterion for capacitor bank sizing is the RMS current rating. The capacitor bank RMS current rating should not result in temperature rise beyond the capacitor rating.

The voltage rating of the resonant capacitor must ensure failsafe operation for all phases in the Qi state machine. During power transfer, the capacitor voltage is low (less than 25 V for 15 W with WRM483265-10F5-12V-G). However, sudden change in coupling when delivering power to load can momentarily increase the load voltage, tank current and hence the capacitor voltage. Though the control loop will eventually bring down the current, the capacitor should not fail for this momentary rise in voltage.

Another scenario to be considered is the capacitor voltage during selection or analog ping. In the selection phase, the tank is excited with pulses at a frequency close to resonant frequency. Though the excitation is of short duration (to ensure the receiver doesn't wake up), the impedance seen by the tank is only coil resistance and capacitor ESR, which could take capacitor voltage to a high value for a short duration. To prevent capacitor failure from voltage stress, the voltage rating should be 100 V. This is in line with data in the Qi specification, where the capacitor voltage is predicted to reach 200 V pk-pk.

The loss in resonant capacitor or capacitor bank is from capacitor ESR:

$$P_{Cr} = I_{TXrms}^{2} \frac{R_{Cr}}{N_{Cr}}$$

Where  $R_{Cr}$  is the ESR of the individual capacitor and  $N_{Cr}$  is the number of capacitors in the bank.

#### 2.2.3 MOSFET selection for inverter stage

The MOSFET voltage rating should be higher than the maximum output of the buck stage output, which includes the buck output OVP level. The current rating should be greater than the peak transmitter coil current value. The MOSFET current rating at the highest case temperature rating should be considered for reliable operation.

$$V_{ds-pk} = \max((1.5 \text{ x } V_{O,buck}), \text{Buck OVP level})$$

$$I_{ds-pk} = I_{TX-pk}$$

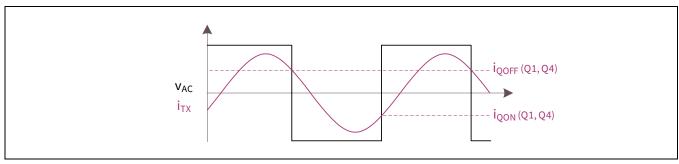

Power loss in the MOSFET is another key parameter that governs the MOSFET part selection. As shown in **Figure 16**, the MOSFET current is negative during turn-on before applying gate pulse resulting in ZVS turn-on. However, the MOSFET turn-off is hard, and is the dominant switching loss. Also, each MOSFET conducts for half of the switching period, based on which the MOSFET parameters for losses are as follows:

$$I_{Qrms} = \frac{I_{TX-pk}}{2}$$

$$P_{cond} = I_{Qrms}^{2} R_{ds(on)}$$

$$P_{SW} = P_{SW-OFF} = \frac{1}{2} V_{O,buck} \; I_{SW,off} \; t_{OFF} \; F_{S-inv}$$

#### Hardware design

The  $t_{OFF}$  computation method remains the same as for the buck converter in section **2.1.4.3**. The turn-off current  $I_{SW,off}$  is the coil current at the instant when the bridge voltage changes polarity. Refer to **Figure 19** for identification of MOSFET currents during turn-on and turn-off from the coil current. The current can be predicted from the model using the tank current magnitude and impedance angle.

Figure 19 Identifying MOSFET turn-on and turn-off from coil voltage and current waveforms

The turn-on switching losses and  $C_{OSS}$  losses are zero due to ZVS action. The time taken to discharge the MOSFET  $C_{OSS}$  depends on the transmitter coil current magnitude at the instant of turn-off of the complementary MOSFET. The dV/dt will be dependent on turn-off current and  $C_{OSS}$  value.

$$\frac{dV}{dt} = \frac{I_{SW,off}}{C_{OSS}}$$

When the dead time is fixed, the  $I_{SW,off}$  quickly discharges the device  $C_{OSS}$  capacitance and the MOSFET body diode conduction starts. The MOSFET is turned on with ZVS when the gate signal is applied. The dead time between gate signals should be large enough to ensure that the drain voltage has discharged  $C_{OSS}$  completely and initiate the body diode conduction.

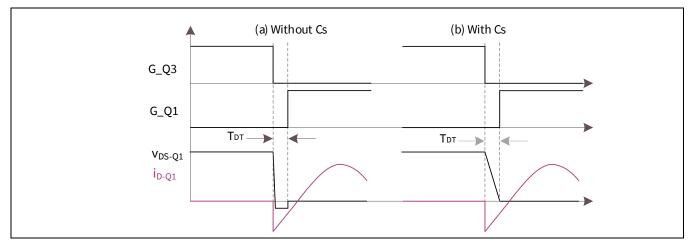

If the settable dead time is high relative to dV/dt, there will be a period where the body diode conducts for a short duration. There is a dead time loss in four MOSFETs, and for power levels like 15 W, the dead time loss has an impact on efficiency. A snubber capacitor ( $C_S$ ) in parallel with one half-bridge device will slow down the dV/dt and ensure minimal body diode conduction, as illustrated in **Figure 20**.

The introduction of  $C_S$  has two advantages. It slows down the dV/dt of MOSFETs thereby reducing emissions, and ensures minimal body diode conduction period for good efficiency.

Figure 20 Impact of snubber capacitor (C<sub>s</sub>) on switching performance

#### Hardware design

The snubber capacitor value is computed so as to bring the switch voltage to zero within the minimum settable dead time for the maximum turn-off current magnitude.

$$C_S = \frac{I_{SW,off-max} T_{DT}}{V_{O,buck}}$$

#### **Gate drive power**

The gate charging and discharging consumes a certain amount of power, which is supplied from the gate driver supply. The gate power is a function of total gate charge and switching frequency:

$$P_{GATE} = Q_G V_{dr} F_S$$

Where:

$V_{dr}$  is the driver supply voltage

$Q_G$  is the gate charge.

The value is available in the datasheet and must be selected for the  $V_{dr}$  level.

#### 2.2.4 Decoupling capacitors

The buck output capacitors are the main DC-link capacitors for the inverter stage. In addition, there are bulk capacitors after buck output CS resistors, and high-frequency noise decoupling capacitors close to the inverter bridge.

The bulk capacitors ensure that the reactive current in the inverter bridge is contained within the inverter stage and is not seen by the buck output capacitors. In this way, the buck output CS resistor sees only the active current drawn by the inverter.

#### 2.3 Control section

WLC1115 in wireless transmitter application for MP-A11 requires minimum external circuitry. In the control section, signal conditioning circuits are required for Q factor estimation and the ASK demodulator along with coil temperature measurement. The WLC1115 requires a standard decoupling capacitor network and bootstrap circuit components to drive the power stage.

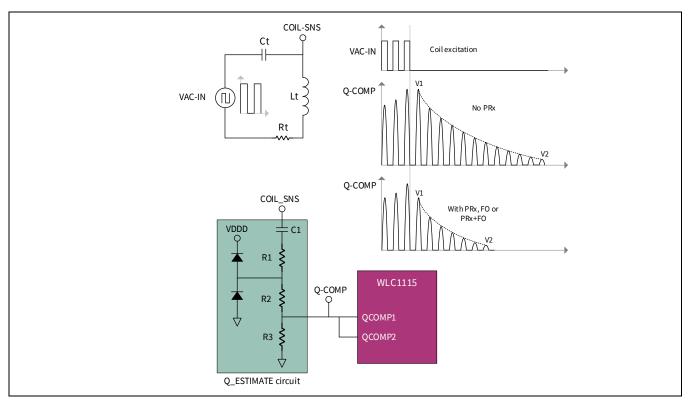

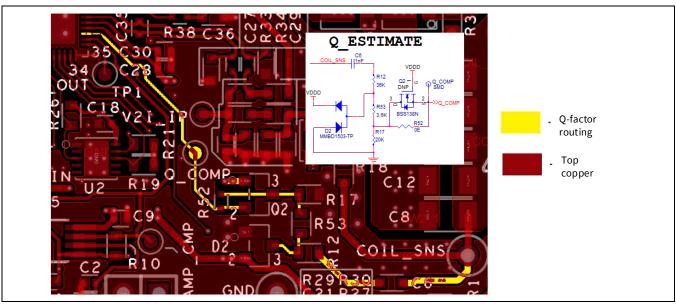

#### 2.3.1 Q factor estimation with WLC1115

WLC1115 uses the coil voltage information to compute the coil Q factor. The presence of Rx or FO or a combination of both before power transfer is reflected in the form of lower Q factor and change in resonance frequency. The primary resonant tank is excited with few pulses and the Q factor and resonant frequency are estimated using the decaying coil voltage waveform, as shown in **Figure 21**. The coil voltage after excitation decays more slowly in the case of no Rx than in the case of Rx or FO present on the interface surface.

#### **Applicable for WLC1115**

# infineon

#### Hardware design

Figure 21 Q factor estimation using WLC1115

The Q factor is calculated from the decaying voltage waveform as:

$$Q = \frac{\pi (t_2 - t_1) F_r}{\ln \left(\frac{V_1}{V_2}\right)} = \frac{\pi N}{\ln \left(\frac{V_1}{V_2}\right)}$$

N is the number of cycles of the decaying waveform between intervals  $t_1$  and  $t_2$ , where  $V_1$  and  $V_2$  are captured and  $F_r$  is the resonant frequency of the primary tank under the influence of the receiver or FO, or both.

The Q factor estimation performed by WLC1115 uses the coil voltage and two comparators. The ZCD comparator produces toggles that are used for resonant frequency calculation.

Refer to the REF\_WLC\_TX15W\_C1 schematics for the Q factor estimation circuit recommended to use with WLC1115. The selection criteria for the components of the Q factor estimation circuit in REF\_WLC\_TX15W\_C1 are as follows:

- 1. The clamping diodes should be of low leakage and low forward drop type. The leakage current of less than 100 nA at the highest operating ambient temperature is ideal. Standard recovery-type diodes rated for more than 100 V suit the application.

- 2. The diode clamping clamps the entire negative half of the coil voltage. The clamping current flows through the diode and R1. Set R1 to have less than 1 mA at the highest operating coil voltage for a low-loss circuit.

- 3. The WLC1115 has an internal pull-down resistor that is disabled only during analog ping and enabled for the rest of the duration.

- 4. R3 value should be approximately half of (R1 + R2).

- 5. R2 value should be slightly lower than (R3  $\parallel$  R<sub>D</sub>).

- 6. C1 along with R1, R2 and (R3 $||R_D|$ ) forms a high-pass filter. Filter bandwidth should be less than the natural resonant frequency.

#### **Applicable for WLC1115**

Hardware design

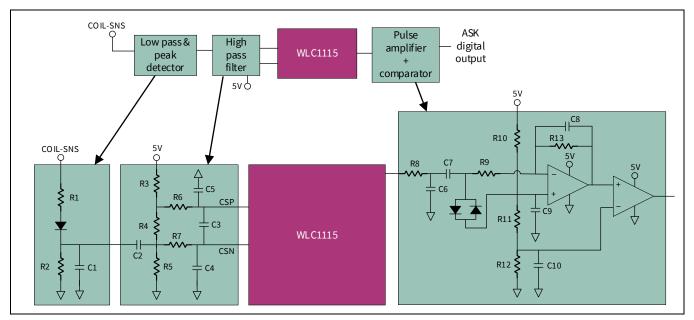

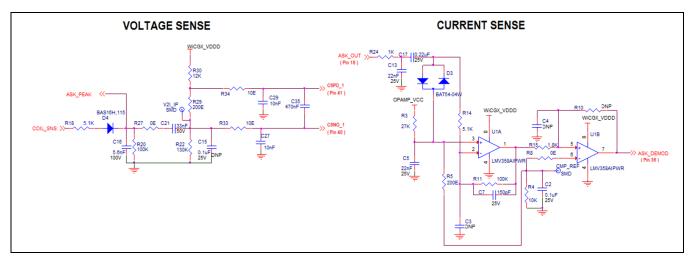

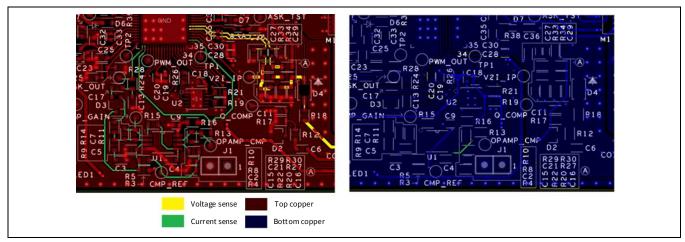

#### 2.3.2 ASK demodulator

The ASK demodulator circuit makes use of coil voltage and inverter bridge input current (or buck output current) to demodulate the data from receiver. The bridge input current feedback is routed to WLC1115 for current measurement. The information from the coil voltage, taken to WLC1115, is derived through some signal conditioning. The demodulated information from both paths is processed through a gain stage followed by a comparator to generate digital data. The configuration used in REF\_WLC\_TX15W\_C1 is shown in Figure 22.

Figure 22 ASK demodulator circuit using WLC1115

The component values are tuned with the following considerations for the REF\_WLC\_TX15W\_C1 and are recommended to use with WLC1115:

- 1. Front-end low-pass filter and peak detector

- a. The negative blocking diode should be rated for the same voltage as the capacitor voltage rating; also, the diode should be of the fast recovery type

- b. The peak charge hold capacitor should also be rated for 100 V

- 2. High-pass filter

- a. The DC blocking capacitor C2 forms a high-pass filter with R5, and the filter bandwidth should be much lower than the ASK communication rate (2 kHz)

- b. Resistor ladder R3, R4 and R5 are selected to ensure 3 V at the CSP and CSN pins

- c. The differential voltage across R4 should be greater than 5 mV

- d. The differential filter formed by (R6 + R7) and C3 should have a bandwidth lower than the switching frequency

- 3. WLC1115 gain settings

- a. For bridge current, the gain is set at 40

- b. For voltage path, gain options range from 40 to 110; set the gain such that the input to amplifier stage is at (VDDD/2) which gives enough headroom for ASK-related swing

- 4. Pulse amplifier and comparator stage

- a. R8 and C6 forms a low-pass filter; the bandwidth should be less than inverter switching frequency but greater than ASK communication frequency

- b. Amplifier gain is set by R9 and R13

- c. Offset to the gain output is set across C9 using R10, R11 and R12; the offset value should be well within the common mode range of the op-amp

#### **Applicable for WLC1115**

#### Hardware design

d. The reference to comparator across C10 is also set using R10, R11 and R12; the reference should be slightly lower than the offset added to the gain stage output, which reduces toggles in comparator output when there is no modulation happening for ASK

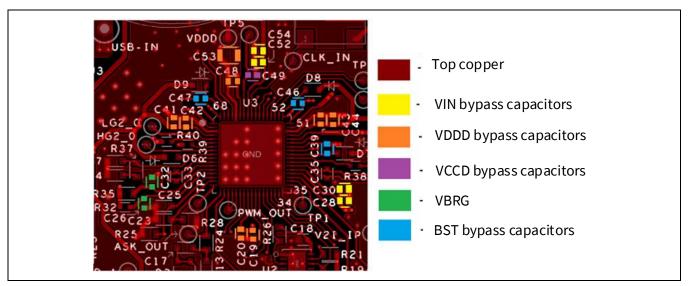

#### 2.3.3 WLC1115-related circuitry

The WLC1115 is a highly integrated controller with inbuilt peripheral and programming flexibility to implement Qi wireless power transmitter design along with USB-PD compatibility. The controller also has an inbuilt low-dropout (LDO) regulator to generate the logic supply (VDDD) and core supply (VCCD), eliminating the need for an auxiliary power supply unit.

Detailed pin descriptions and external requirements for each pin are listed in the datasheet [2].

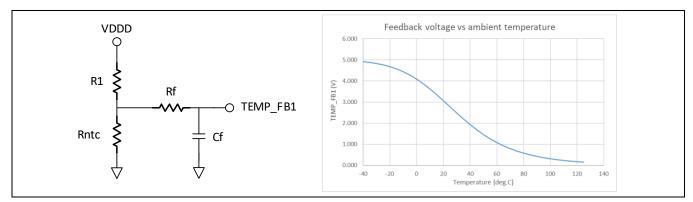

#### 2.3.4 NTC feedback

The NTC monitors the transmitter unit temperature and is placed close to the coil. The NTC, when mounted on the interface surface, can be used to detect temperature rise in the interface surface from the heat radiated from the FO. The NTC feedback interface to WLC1115 ADC is a simple divider network with a filter, as shown in **Figure 23**. The NTC resistance is a function of temperature, and the accurate NTC resistance temperature characteristics are provided by the manufacturer (the characteristics can also be generated from NTC parameters, but the manufacturer-provided values account for non-linearities). The feedback to WLC1115 for the REF\_WLC\_TX15W\_C1 is shown in **Figure 23**.

Figure 23 NTC interface to WLC1115 and NTC feedback value with temperature for REF\_WLC\_TX15W\_C1

Design considerations:

- 1. The series resistor should ensure that the current in NTC at any temperature doesn't lead to a power loss greater than NTC specified value

- 2. The low-pass filter in the feedback path should have bandwidth low enough to discard the switching noise and ASK modulator frequency

- 3. Good resolution in feedback around required trip and recovery points

#### 2.3.5 System configuration for PD sink compliance

WLC1115 has an integrated USB Type-C PD controller and complies to the latest USB Type-C and PD specifications. The bulk capacitance between the USB input (also referred to as VBUS) and ground result in large inrush current. The USB-PD specifications mandate the sink to limit the input inrush current at attach. To comply with the inrush current requirements of the transmitter unit, WLC1115 has an integrated high voltage gate driver to drive a consumer NFET on VBUS. The gate driver has a slow turn-on feature, which can be used to avoid a sudden inrush of current.

#### Hardware design

Select a low R<sub>DS(on)</sub> MOSFET for low conduction losses. This MOSFET works as a load switch and will not have any switching losses. Use the NFET\_CTRL\_1 pin of WLC1115 (pin 35) to drive the consumer NFET.

#### 2.3.6 Other circuits

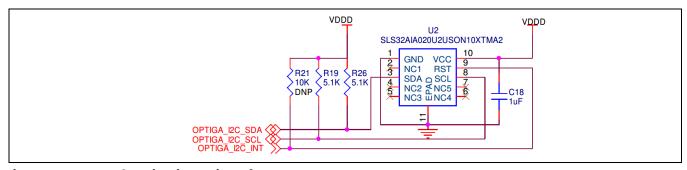

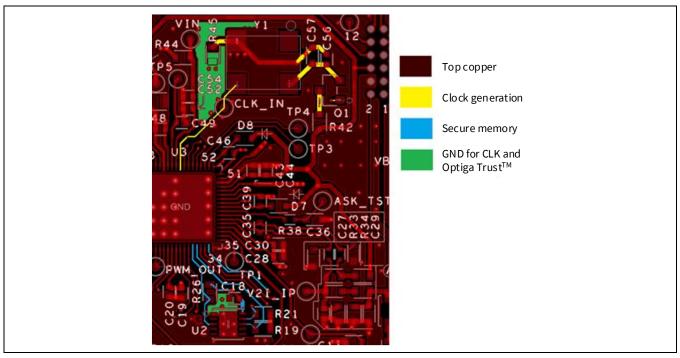

The authentication requirements for Qi v1.3.2 is realized using a security controller from Infineon. The OPTIGA™ Trust comes with full system integration for simple and cost-effective deployment of authentication. The OPTIGA™ Trust (U2) interface with WLC1115 is through I²C protocol (**Figure 24**) along with a control line for OPTIGA™ chip reset. The SCL and SDA have pull-up resistors for the I²C lines.

Figure 24 Authentication IC interface

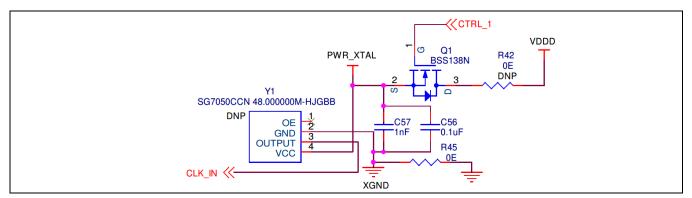

WLC1115 has an internal oscillator whose tolerance meets the Qi requirements for FSK. An optional external oscillator (for more accurate clock or any proprietary FSK implementation) can be interfaced to WLC1115 through pin 60. The oscillator needs to operate at VDDD level and should be placed close to WLC1115. To reduce standby power, the bias to the oscillator can be disconnected through Q1, which is driven directly by WLC1115.

Figure 25 External oscillator interface (optional)

Design example - 15 W transmitter board

#### 3 Design example – 15 W transmitter board

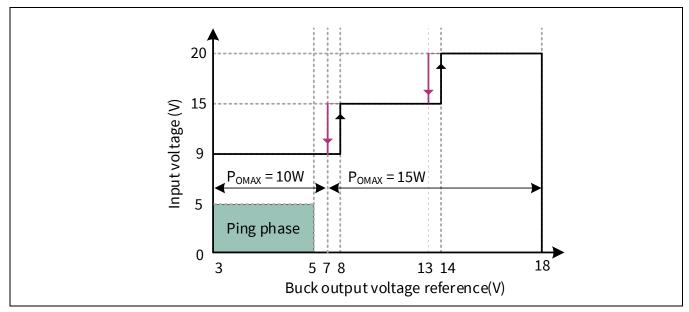

This section presents a design example for the 15 W wireless charger transmitter board, the specifications of which match the REF\_WLC\_TX15W\_C1. The design example assumes buck stage operation with variable input control. The input voltage is configurable to three voltages on buck output voltage reference. The behavior is captured in **Figure 26**.

The key specifications of the power stage are as follows:

- Input voltage: 9 V, 15 V or 20 V during PD; 5 V during ping stage

- Buck stage output voltage: Up to 18 V

- Receiver output power: Maximum 15 W

- Buck stage switching frequency: 400 kHz

- Inverter stage switching frequency: 127.7 kHz

#### **Design parameters**

- Buck inductor ripple current: 1.5 A peak to peak

- Overload factor: 150 percent

- Input voltage ripple: 1 percent

- Buck output voltage ripple: 2 percent

- Allowed dip in buck output voltage: 5 percent of output

- Buck control-loop bandwidth: 25 kHz

Figure 26 Variable PD input scheme for the buck stage

The buck power stage components calculation is listed in **Table 3**. Based on the computed values, the BOM for key components is listed in **Table 6**. For the Q factor estimation and ASK demodulator circuit, refer to the component values from REF\_WLC\_TX15W\_C1 schematics in [3].

Design example - 15 W transmitter board

**Buck and inverter power stage component calculation** Table 3

| Parameter                 | Formula                                                                                                                                                                                  | Calculated value                                                                                                                                                                       | Remarks                                                                                                                                                                                                                                       |  |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Inductance value          | $L = \frac{V_{in}D(1-D)}{F_S\Delta i_L}$                                                                                                                                                 | 7.58 μH for 20 V input                                                                                                                                                                 | Maximum inductance value across the operating points                                                                                                                                                                                          |  |

| Inductor current          | $I_{Lrms} = \sqrt{I_0^2 + \left(\frac{\Delta i_L}{2\sqrt{3}}\right)^2}$ $I_{Lpk} = (1.5 \times I_0) + \frac{\Delta i_L}{2}$                                                              | $I_{Lrms} = 2.51 A$ $I_{Lpk} = 4.12 A$                                                                                                                                                 | The currents are for 6.8 µH standard inductance value and maximum value across the working conditions                                                                                                                                         |  |

| Input capacitor           | $C_{IN} > \frac{I_{IN}(1-D)}{\Delta V_{in} F_S}$ $I_{CIN_{rms}} = \sqrt{D\left(I_0^2(1-D) + \frac{\Delta i_L^2}{12}\right)}$                                                             | 15.43 $\mu$ F for 9 V input<br>8.89 $\mu$ F for 15 V input<br>3.28 $\mu$ F for 20 V input<br>$I_{CIN_{rms}} = 1.19 A$                                                                  | ${\cal C}_{IN}$ computed for $\Delta {\cal V}_{in}$ of 1 percent of ${\cal V}_{in}$ Ripple current is the maximum across the operating points                                                                                                 |  |

| Output capacitor          | $C_{O1} = \frac{\Delta t_L}{8 F_S \Delta V_O}$ $C_{O2} = \frac{I_{O_{Step}}}{V_{Odip}} \frac{1}{2\pi F_{BW}}$ $C_O = \max(C_{O1}, C_{O2})$ $I_{CO_{rms}} = \frac{\Delta t_L}{2\sqrt{2}}$ | $C_O$ values<br>53.05 $\mu$ F for 6 V<br>output<br>15.92 $\mu$ F for 12 V<br>output<br>9.55 $\mu$ F for 15 V<br>output<br>7.96 $\mu$ F for 18 V<br>output<br>$I_{CO_{rms}} = 0.48$ $A$ | $C_{O1}$ computed for $\Delta V_{O} = 2$ percent of $V_{O}$ $C_{O2}$ values computed for $F_{BW}$ of 25 kHz, $V_{Odip} = 5$ percent of $V_{OUT}$ and $I_{O_{Step}} = 1.5$ x $I_{O}$ Ripple current is the maximum across the operating points |  |

| Buck stage<br>MOSFETs     | $V_{dspk} = \max \left( (1.5V_{in-op}), V_{in-withstand} \right)$ $I_{ds-pk} = I_{Lpk} = (1.5 \times I_0) + \left( \frac{\Delta i_L}{2} \right)$                                         | $V_{donk} = 30 V$                                                                                                                                                                      | Values are the worst-case<br>across the operating points                                                                                                                                                                                      |  |

| Input CS shunt            | $R_{Sh_{in}} = 0.005\Omega$ $P_{RSh_{in}} = I_{Qrms_{HS}}^{2} R_{Sh_{in}}$                                                                                                               | $P_{Rsh_{in}} = 0.021 W$                                                                                                                                                               | Shunt value as per WLC1115 requirement                                                                                                                                                                                                        |  |

| Output CS shunt           | $R_{sh_o} = 0.010\Omega$ $P_{Rsh_o} = I_O^2 R_{sh_o}$                                                                                                                                    | $P_{Rsh_o} = 0.063 W$                                                                                                                                                                  | Computed loss is the worst-<br>case value across the operating<br>points                                                                                                                                                                      |  |

| Transmitter coil          | $L_{tx} = 6.3uH$                                                                                                                                                                         | $I_{TXrms} = 3.66 \text{ A}$                                                                                                                                                           | Inductance and capacitance values as per Qi Standard [1] Values based on actual measurements from three test receivers                                                                                                                        |  |

| Resonant cap              | $C_r = 500nF$                                                                                                                                                                            | $I_{Cr,rms} = 3.66 \mathrm{A}$                                                                                                                                                         |                                                                                                                                                                                                                                               |  |

| Inverter stage<br>MOSFETs | $\begin{vmatrix} V_{ds-pk} \\ = \max \left( (1.5 \times V_{O,buck}), \text{Buck OVP} \right) \\ I_{ds-pk} = I_{TX-pk} \end{vmatrix}$                                                     | $V_{ds-pk} = 27 \text{ V}$ $I_{ds-pk} = 5.45 \text{ A}$                                                                                                                                | Values based on actual<br>measurements from three test<br>receivers                                                                                                                                                                           |  |

| Snubber capacitors        | $C_S = \frac{I_{SW,off-max} T_{DT}}{V_{O,buck}}$                                                                                                                                         | $C_S = 10.8  nF$                                                                                                                                                                       | Maximum value from data of three receivers                                                                                                                                                                                                    |  |

#### Design example - 15 W transmitter board

**Table 3** sets out the values and requirements for the power stage components. The selection of parts depends on factors such as performance, losses, cost, etc., and might also need a few iterations. As an example, part selection for buck stage input capacitor and buck stage MOSFETs is shown in **Table 4** and **Table 5**, respectively. Based on a similar approach for other components, a high-level BOM for the design example is captured in **Table 6**.

| Table 4 Part selection example – buck stage input ca |

|------------------------------------------------------|

|------------------------------------------------------|

| Capacitor     | Voltage rating – 25 V or above                                                                              |

|---------------|-------------------------------------------------------------------------------------------------------------|

| requirements  | Capacitance value and ripple current rating as in Table 3.                                                  |

|               | CL31X106KAHNNNE                                                                                             |

|               | Rating – 10 μF 25 V                                                                                         |

| Option 1      | Number of capacitors required – <b>5</b> (to meet $C_{IN}$ and $I_{CIN_{rms}}$ across the operating points) |

|               | Capacitor bank capacitance value – 22.02 μF at 9 V, 10.61 μF at 15 V and 8.77 μF at 20 V                    |

|               | input capacitor bank ripple current rating – 11.9 A <sub>RMS</sub> for 10°C temperature rise                |

|               | CL31X226KAHN3NE                                                                                             |

|               | Rating – 22 μF 25 V                                                                                         |

| Ontion 2      | Number of capacitors required – <b>2</b> (to meet $C_{IN}$ and $I_{CIN_{rms}}$ across the operating points) |

| Option 2      | Capacitor bank capacitance value – 20.45 μF at 9 V, 10.49 μF at 15 V and 8.09 μF at 20 V                    |

|               | input                                                                                                       |

|               | Capacitor bank ripple current rating – 5.6 A <sub>RMS</sub> for 10°C temperature rise                       |

| C - l t l t   | CL31X226KAHN3NE – considering the part count and associated impact on cost and area                         |

| Selected part | occupied in PCB                                                                                             |

#### Table 5 Part selection example – buck stage MOSFETs

| MOSFET        | Voltage rating – 30 V                                                                     |  |  |

|---------------|-------------------------------------------------------------------------------------------|--|--|

| requirements  | Current rating – 4.12 A                                                                   |  |  |

|               | BSZ0910LSATMA1                                                                            |  |  |

|               | Rating – 30 V, 40 A, 5.7 m $\Omega$                                                       |  |  |

|               | Power loss (from equations in sections 2.1.4.1 to 2.1.4.4) for 15 V input 7 V output 15 W |  |  |

| Option 1      | load on buck converter                                                                    |  |  |

|               | Q_HS losses – 165 mW (inclusive of conduction, switching and recovery), 17 mW gate drive  |  |  |

|               | Q_LS losses – 38 mW (inclusive of conduction, switching and dead time losses) 17 mW gate  |  |  |

|               | drive                                                                                     |  |  |

|               | ISZ065N03L5S                                                                              |  |  |

|               | Rating – 30 V, 40 A, 8.6 m $\Omega$                                                       |  |  |

|               | Power loss (from equations in sections 2.1.4.1 to 2.1.4.4) for 15 V input 7 V output 15 W |  |  |

| Option 2      | load on buck converter                                                                    |  |  |

|               | Q_HS losses – 174 mW (inclusive of conduction, switching and recovery), 10 mW gate drive  |  |  |

|               | Q_LS losses – 54 mW (inclusive of conduction, switching and dead time losses) 10 mW gate  |  |  |

|               | drive                                                                                     |  |  |

| Selected part | BSZ0910LSATMA1 – considering the losses, which is a key aspect of buck stage              |  |  |

Design example - 15 W transmitter board

Table 6 Key components BOM for the design example

| Function                                      | Qty | Description                                                                                              | Part number                   | Manufacturer                  |

|-----------------------------------------------|-----|----------------------------------------------------------------------------------------------------------|-------------------------------|-------------------------------|

| Wireless controller                           | 1   | Wireless transmitter with integrated USB Type-C PD controller 68-pin QFN                                 | WLC1115-68LQXQ                | Infineon Technologies         |

| Buck and inverter stage MOSFETs               | 6   | N-channel 30 V 18 A ( $T_a$ ), 40 A ( $T_c$ ) 2.1 W ( $T_a$ ), 37 W ( $T_c$ ) surfacemount PG-TDSON-8 FL | BSZ0910LSATMA1                | Infineon Technologies         |

| Buck stage inductor                           | 1   | Fixed inductor 6.8 $\mu$ H 6.5 A 17.6 $m\Omega$                                                          | PA4342.682NLT                 | Pulse Electronics<br>Power    |

| Buck stage current shunt                      | 1   | Resistor 0.005 Ω 1% 1 W 1206                                                                             | LVT12R0050FER                 | Ohmite                        |

| Buck stage input bulk capacitors              | 2   | Ceramic capacitor 22 µF 25 V<br>X6S 1206                                                                 | CL31X226KAHN3NE               | Samsung Electro-<br>Mechanics |

| Buck output bulk capacitors                   | 4   | Ceramic capacitor 22 µF 25 V<br>X6S 1206                                                                 | CL31X226KAHN3NE               | Samsung Electro-<br>Mechanics |

| Inverter stage current shunt                  | 1   | Resistor 0.01 Ω 1% 1 W 1206                                                                              | LVT12R0100FER                 | Ohmite                        |

| Inverter input bulk capacitors                | 2   | Ceramic capacitor 22 μF 25 V<br>X5R 0805                                                                 | CC0805MKX5R8BB226             | Yageo                         |